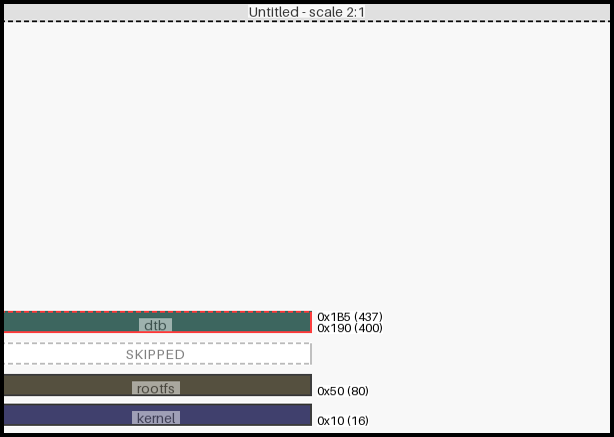

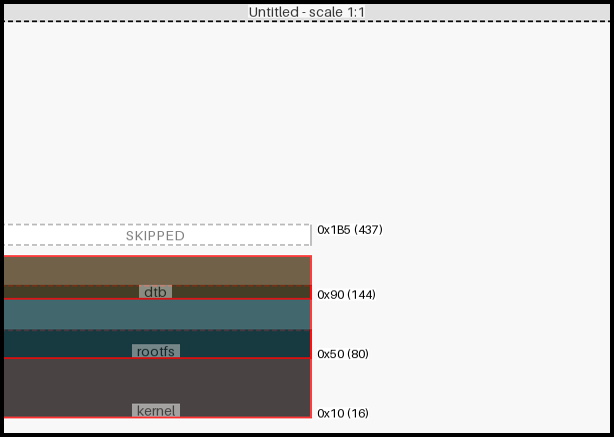

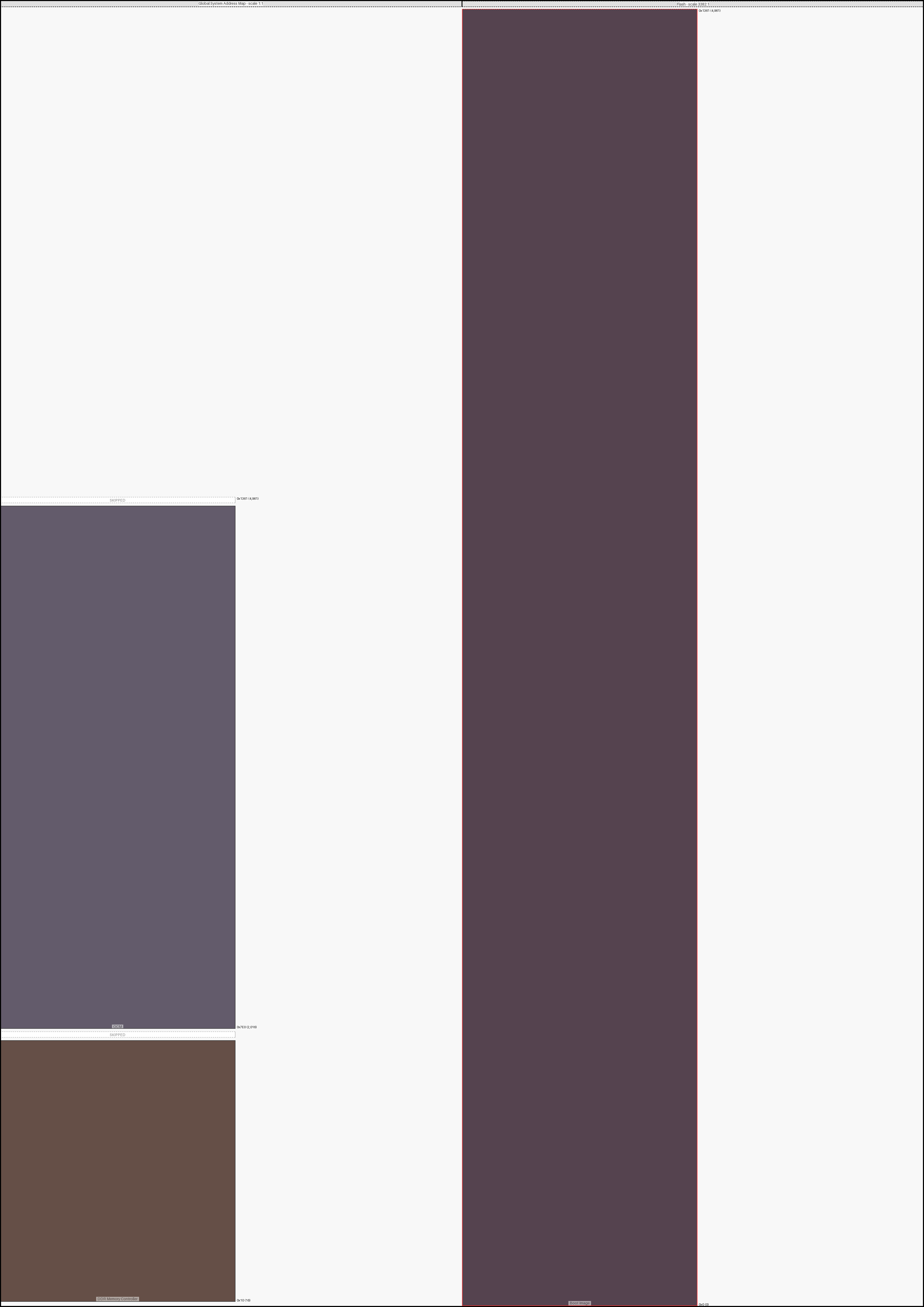

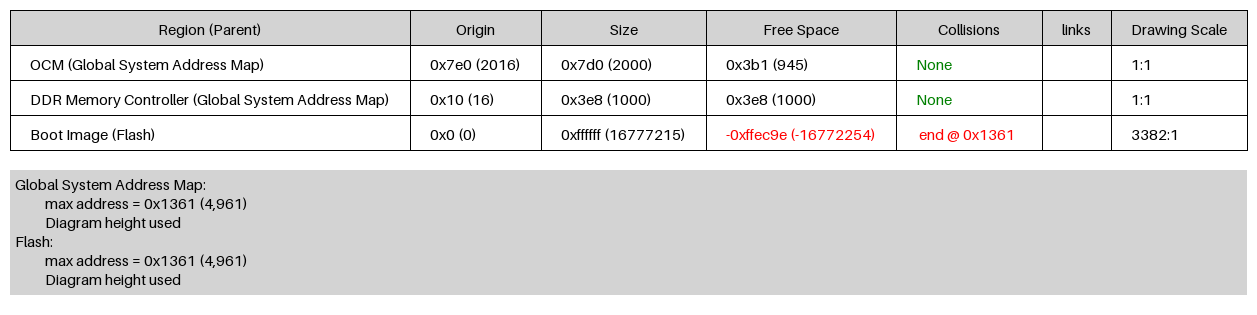

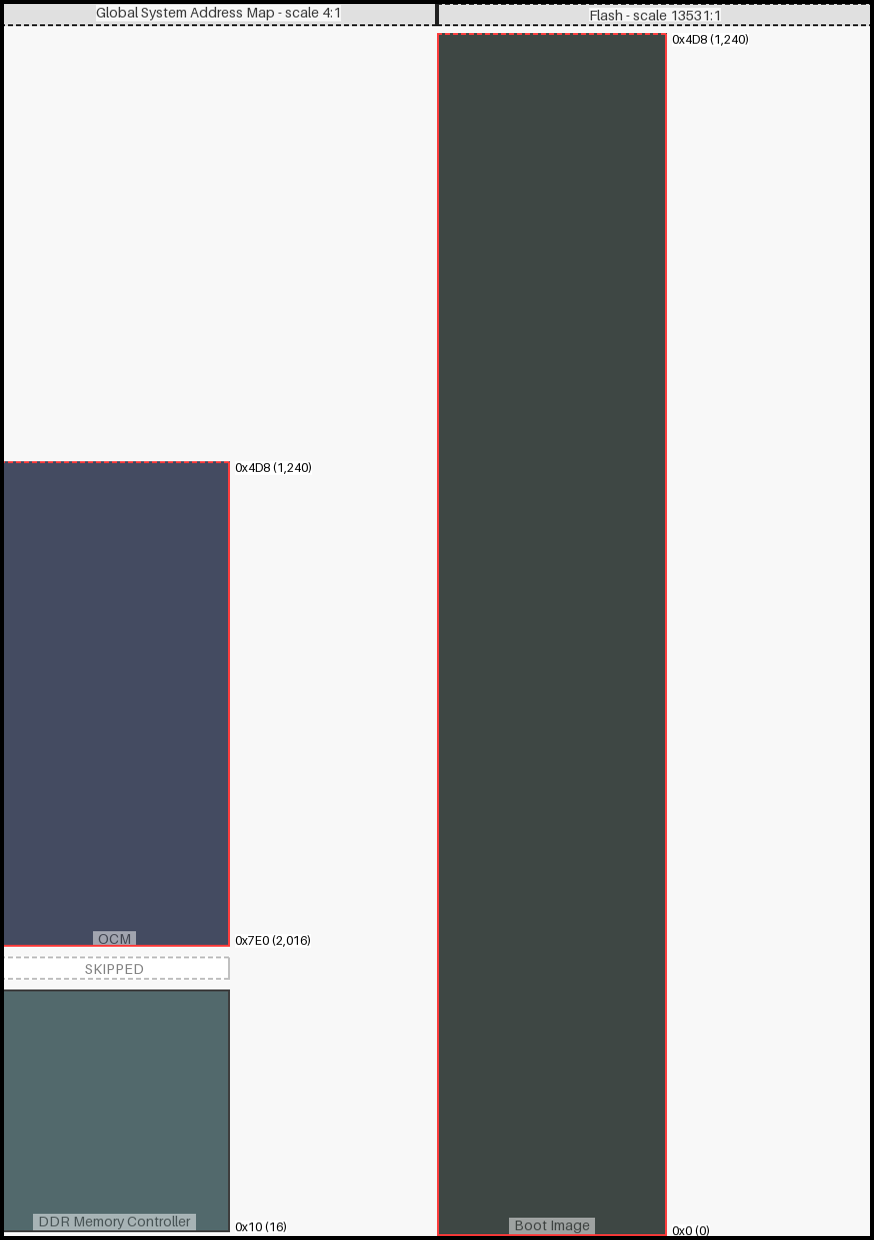

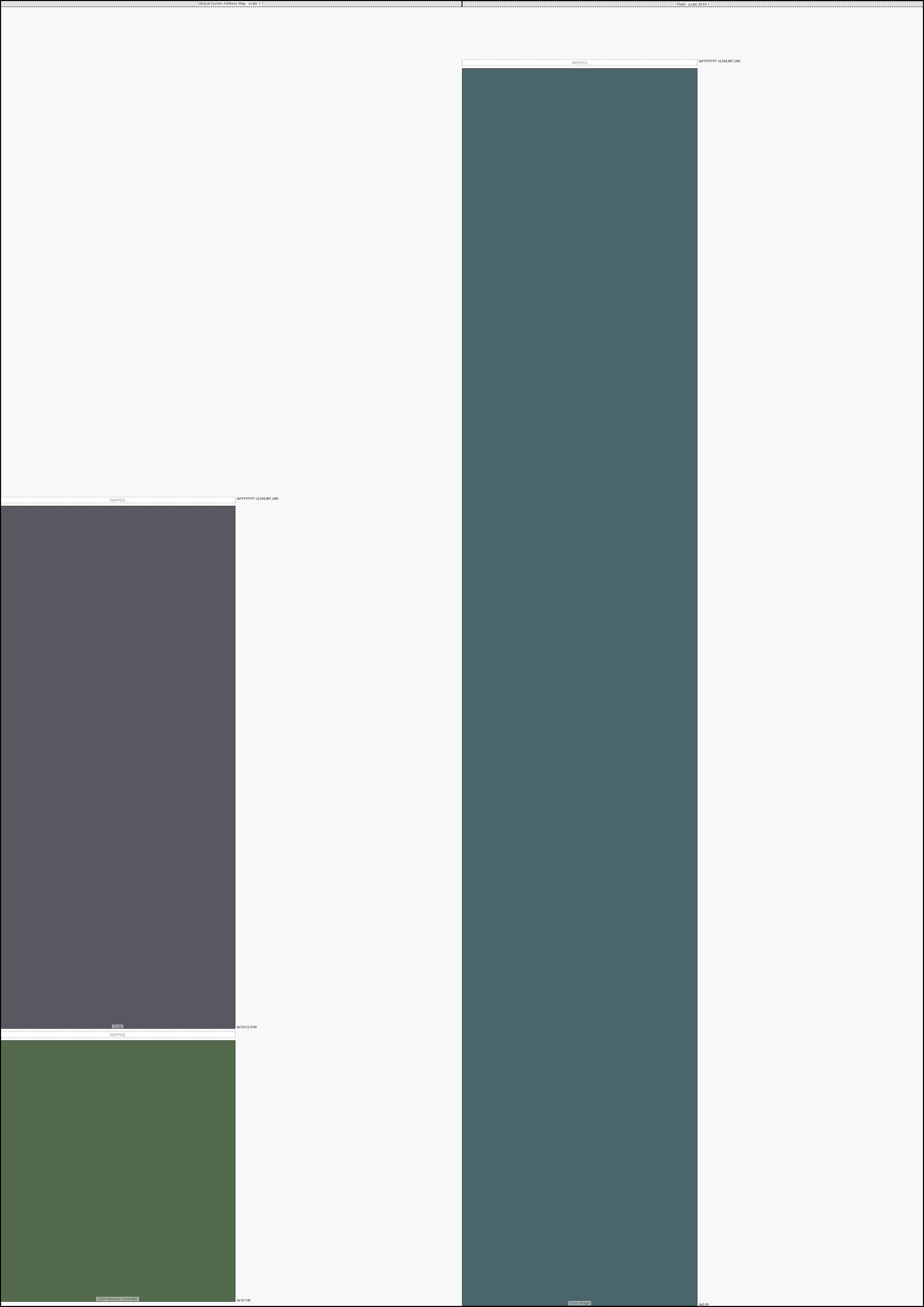

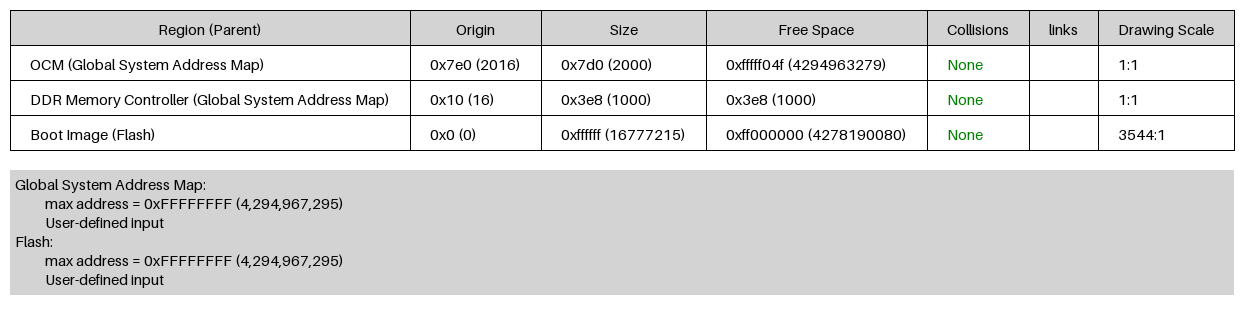

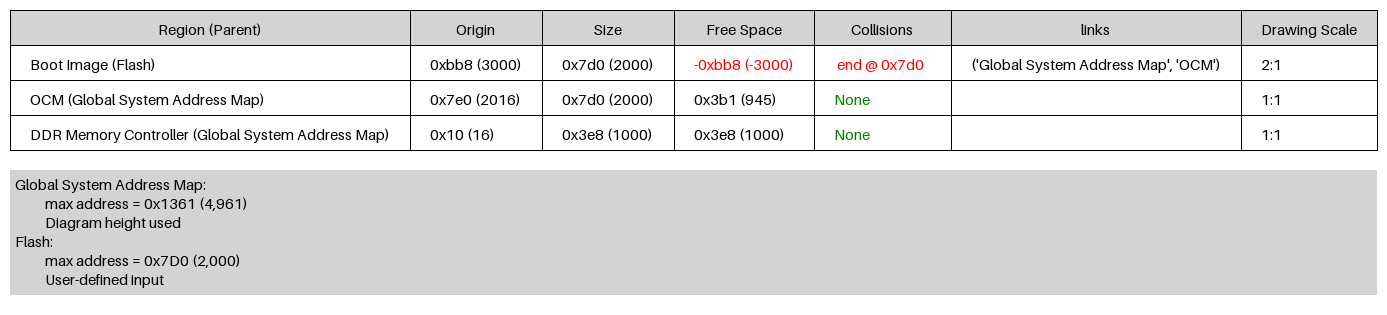

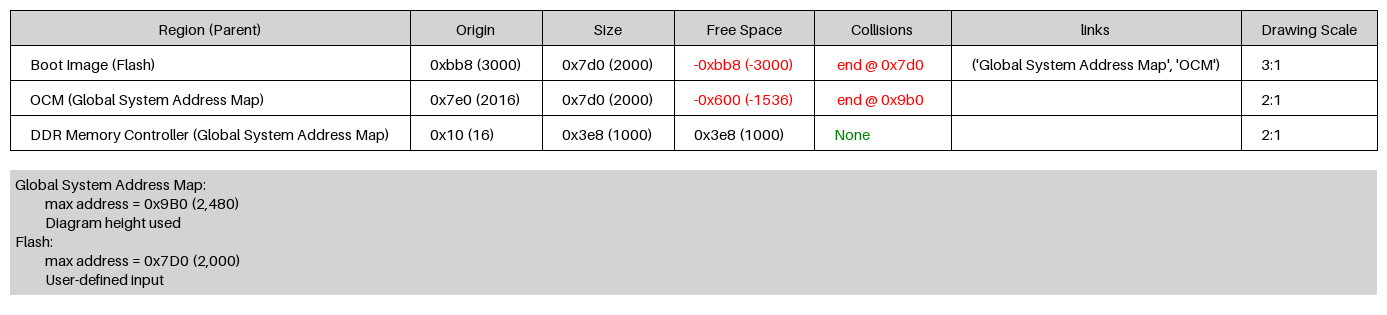

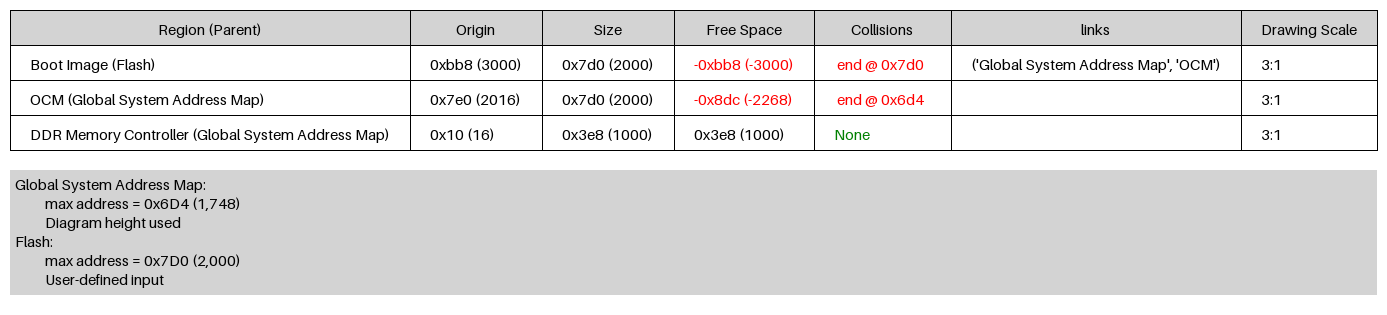

docs/example/example_end_collisions |

| Region collision with diagram max address |

|

|

docs/example/example_end_collisions.json

{

|

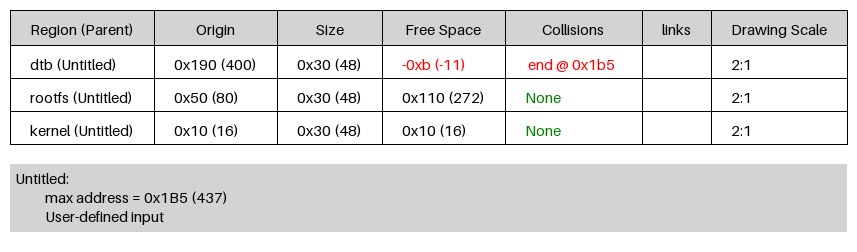

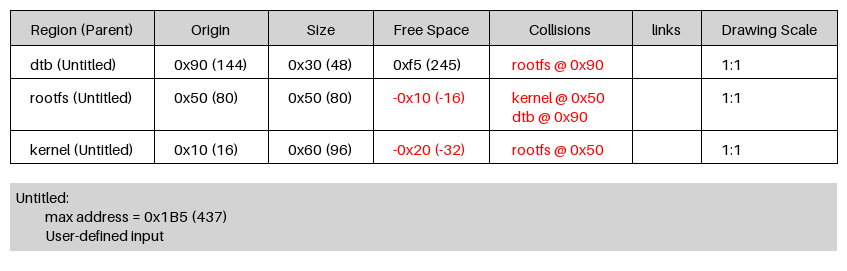

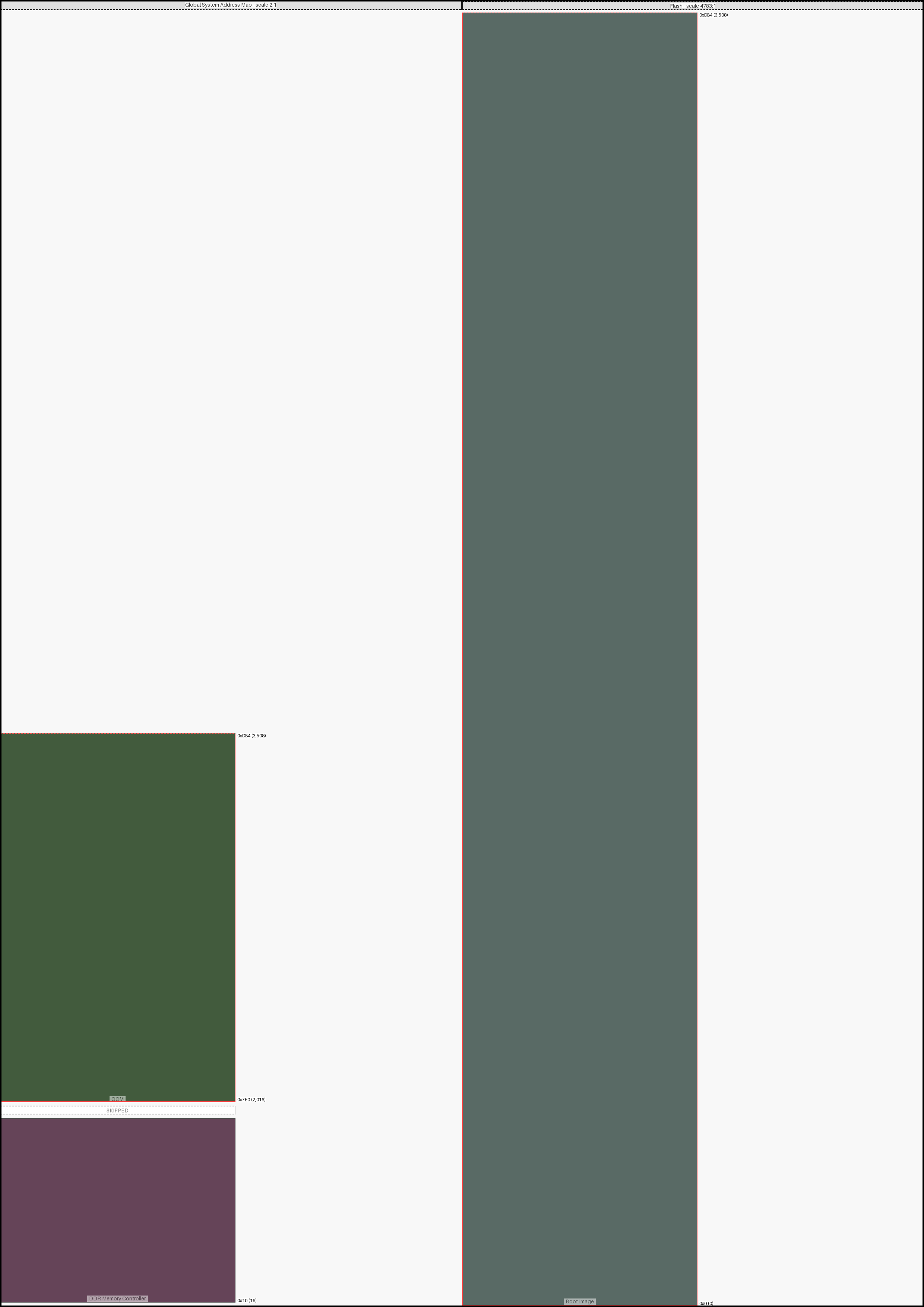

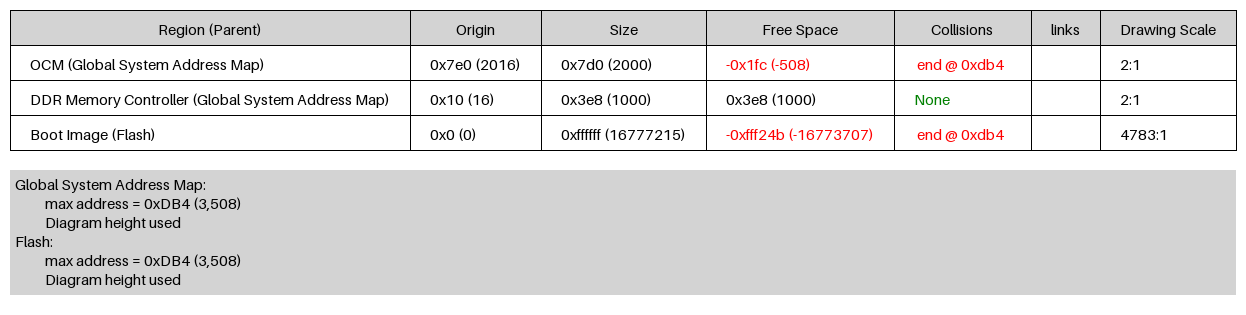

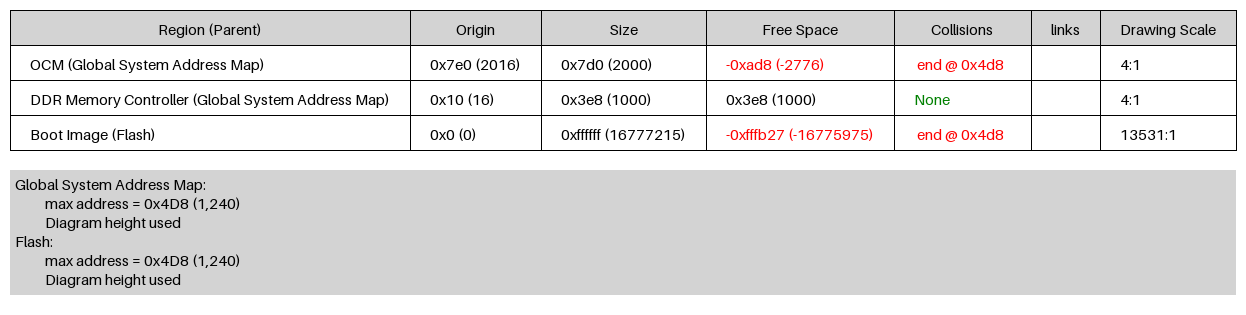

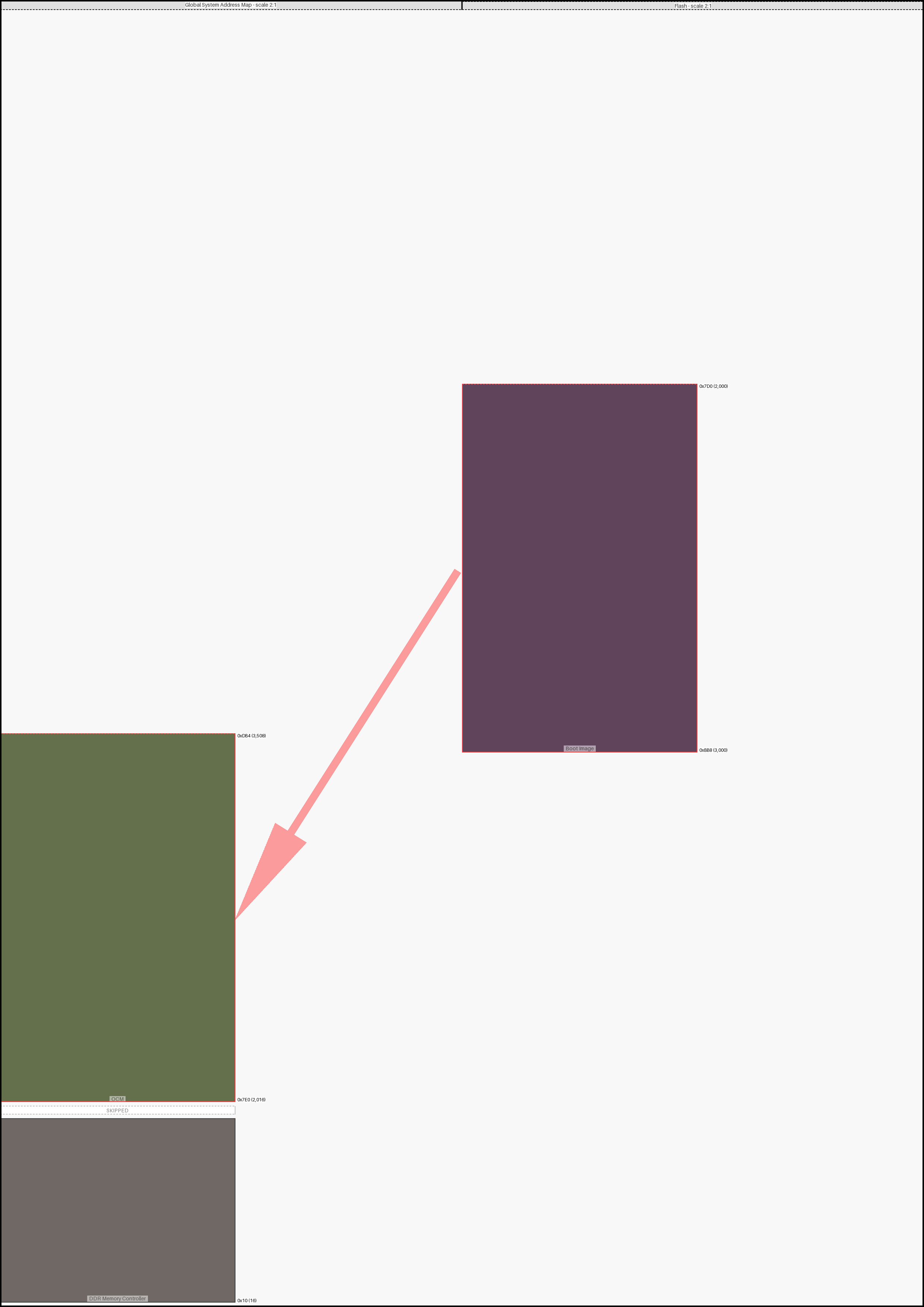

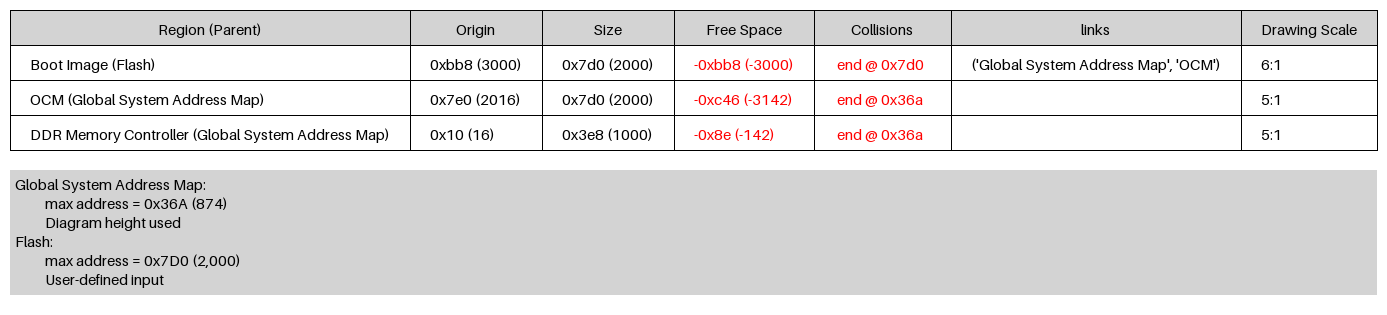

docs/example/example_region_collisions |

| Region collisions with other regions |

|

|

docs/example/example_region_collisions.json

{

|

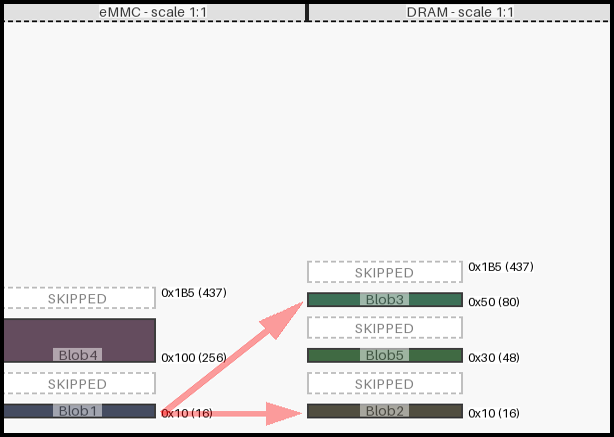

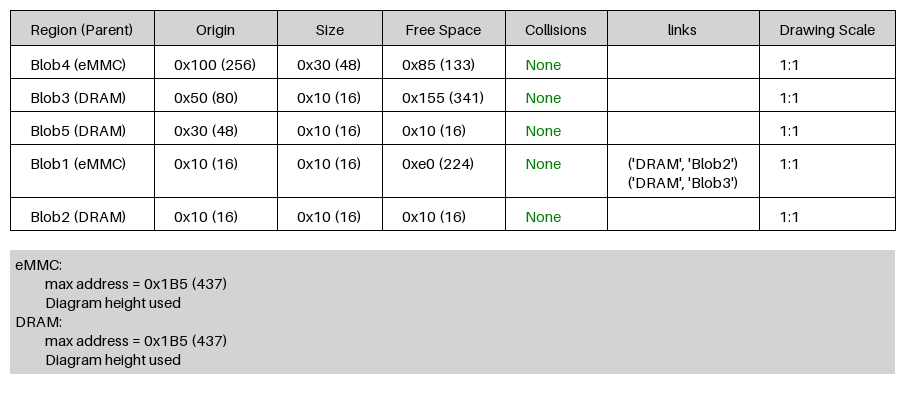

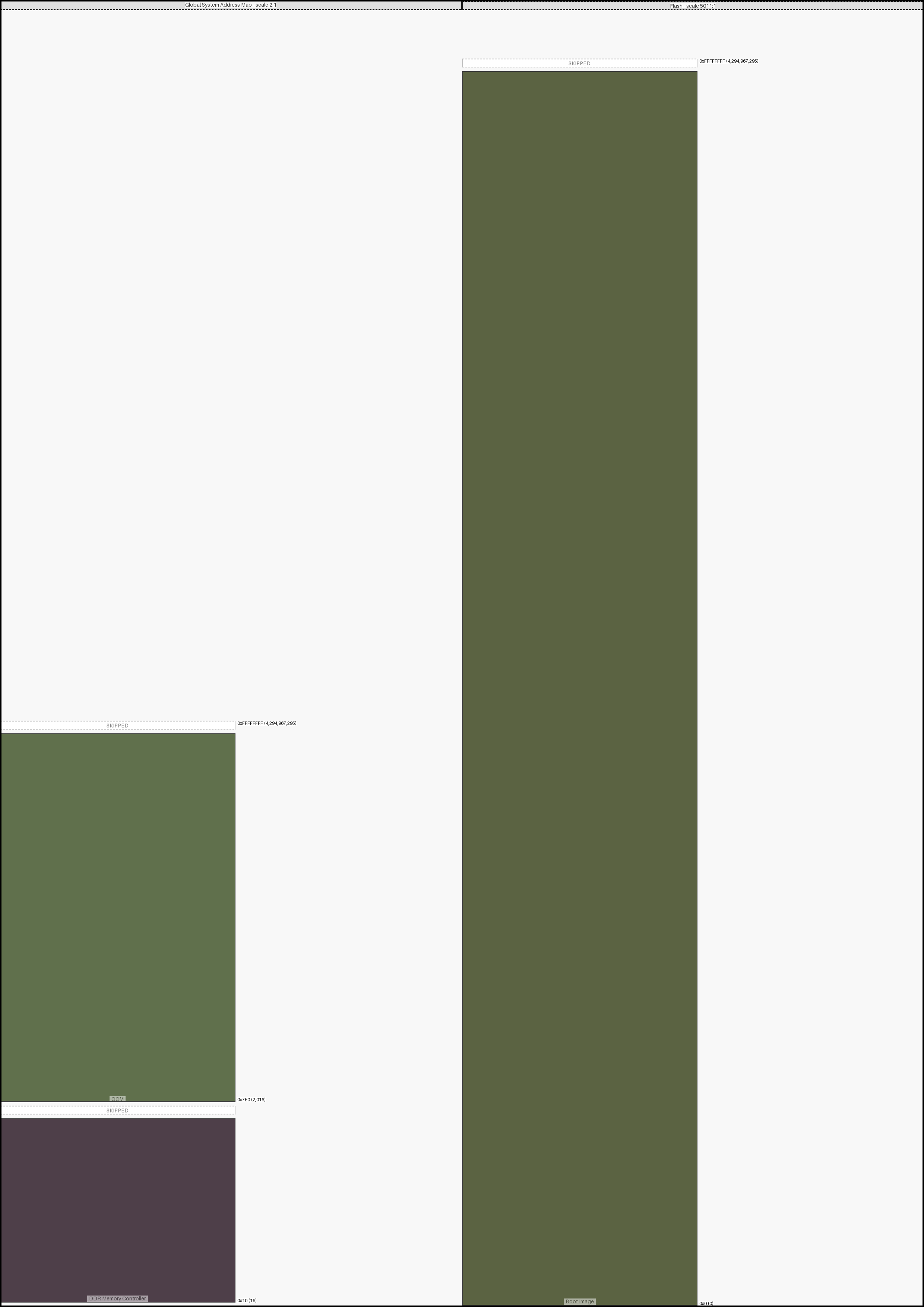

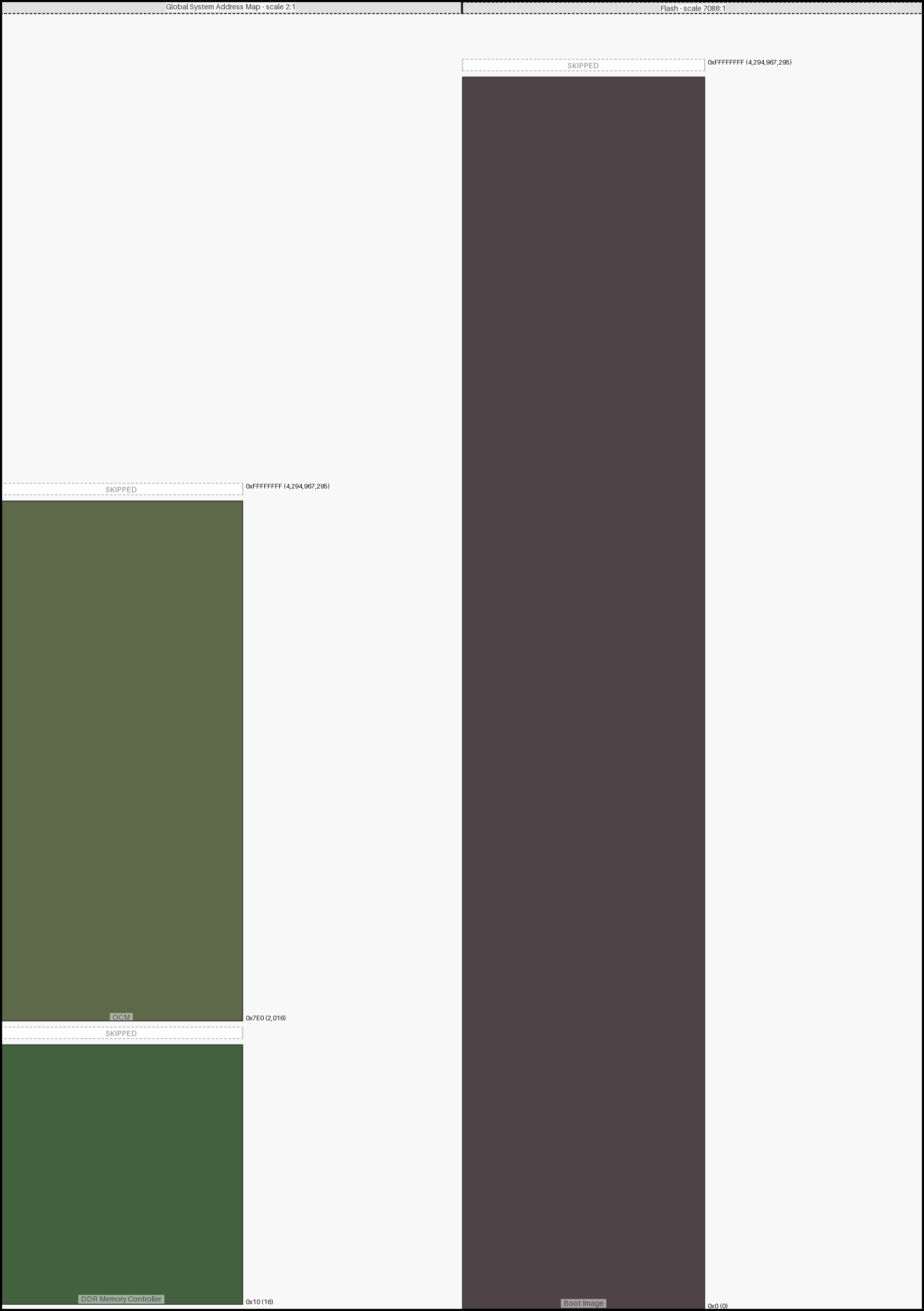

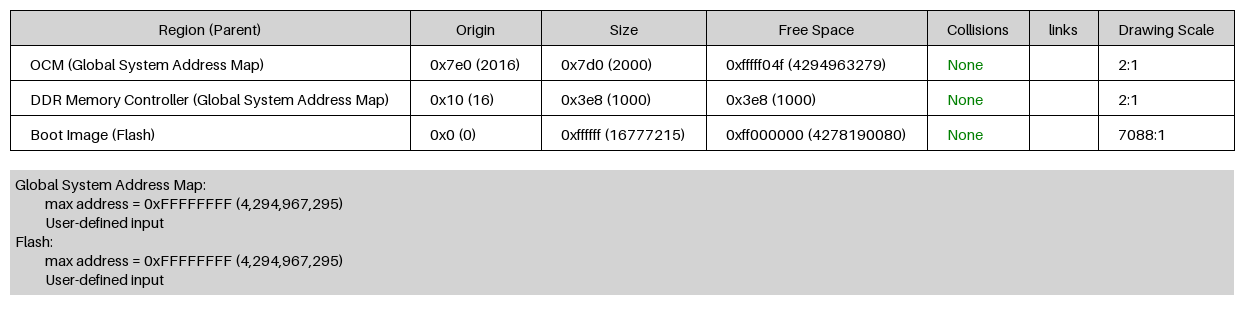

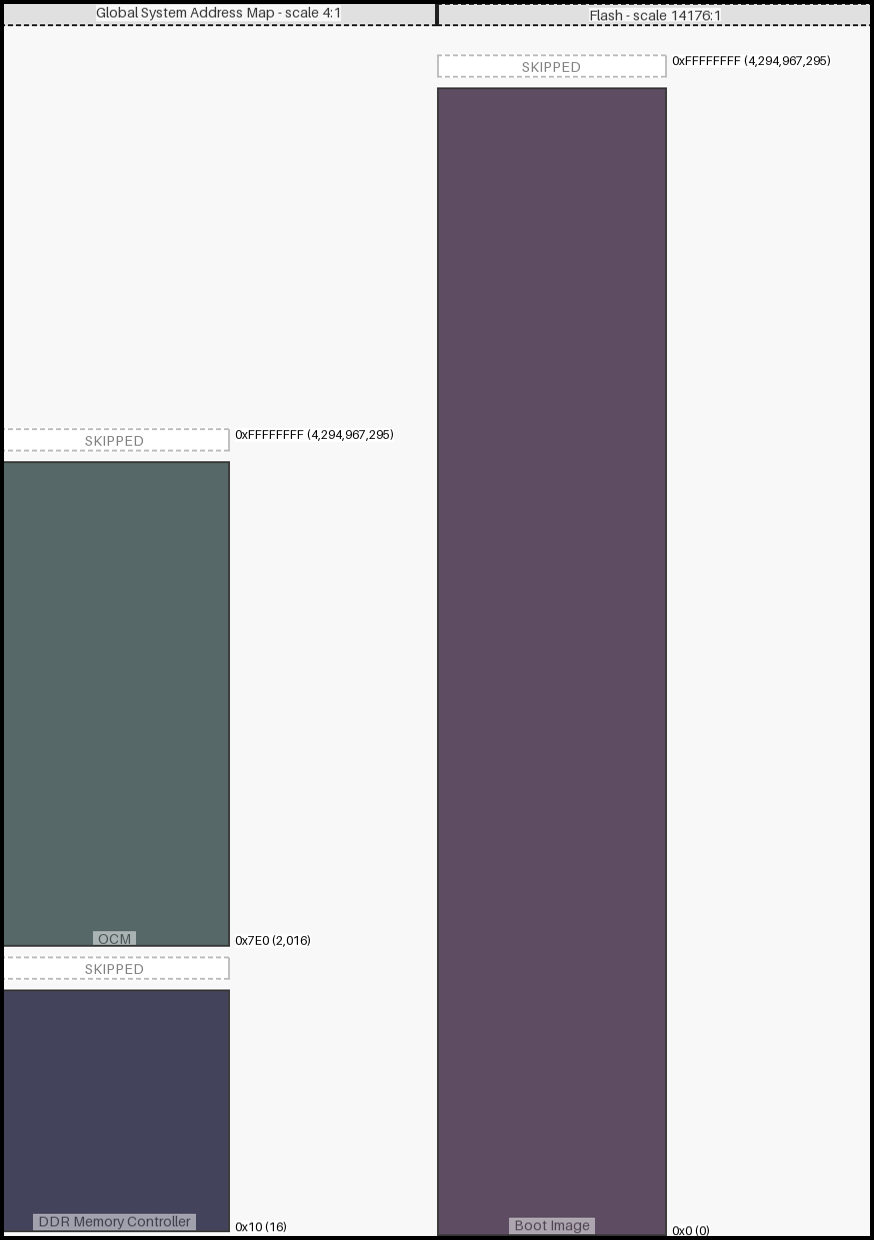

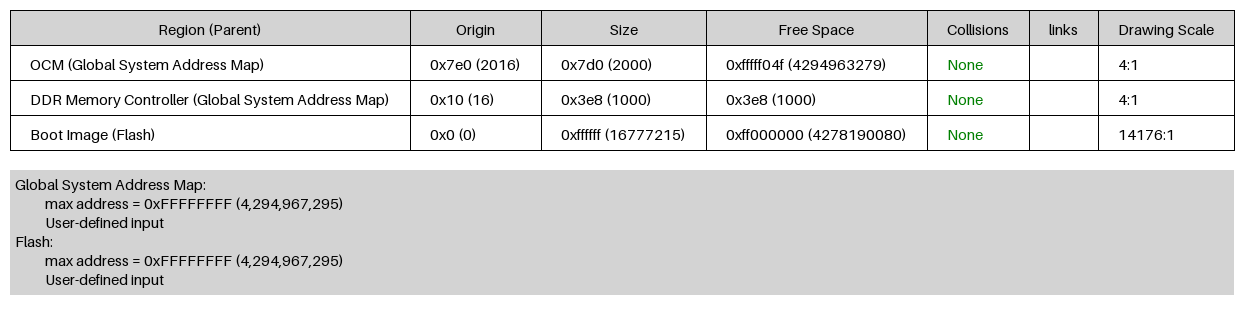

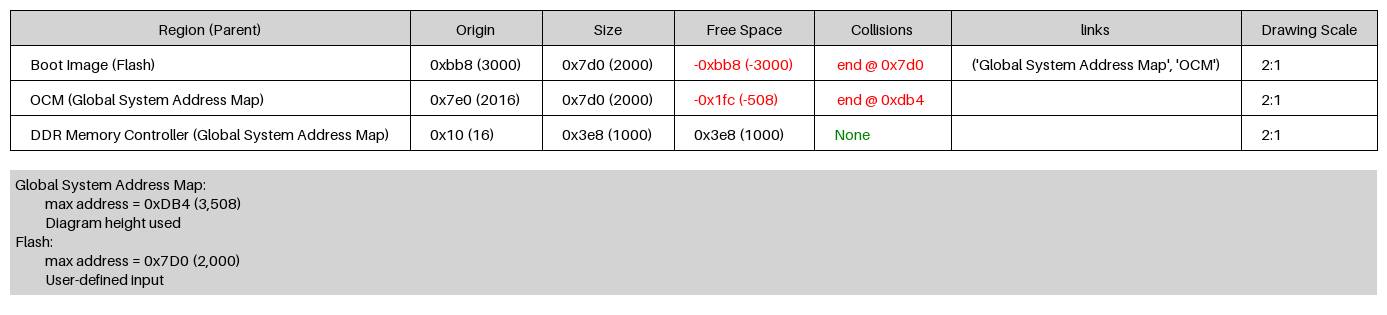

docs/example/example_two_maps |

| Diagram with two memory maps |

|

|

docs/example/example_two_maps.json

{

|

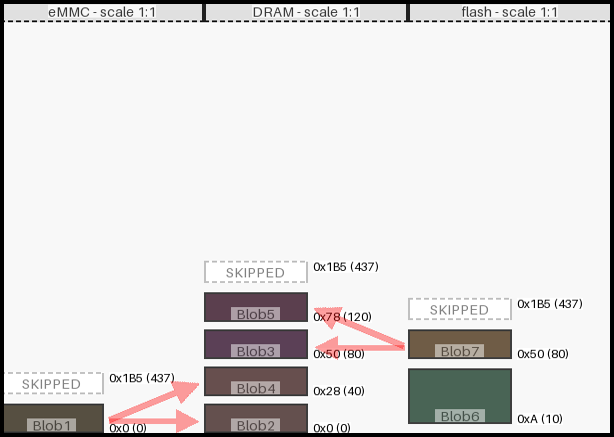

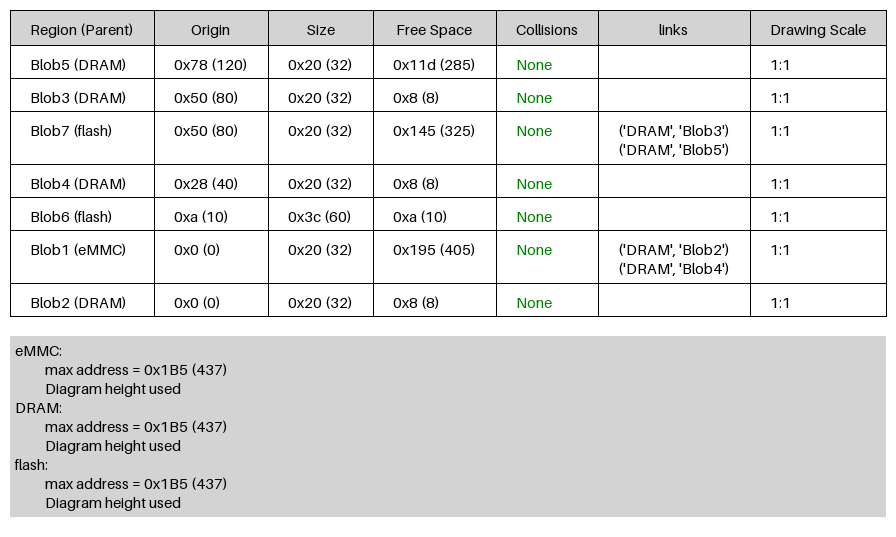

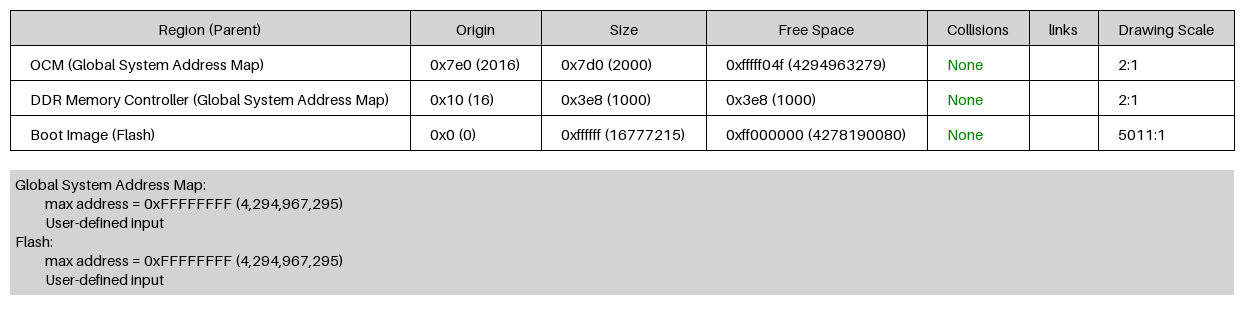

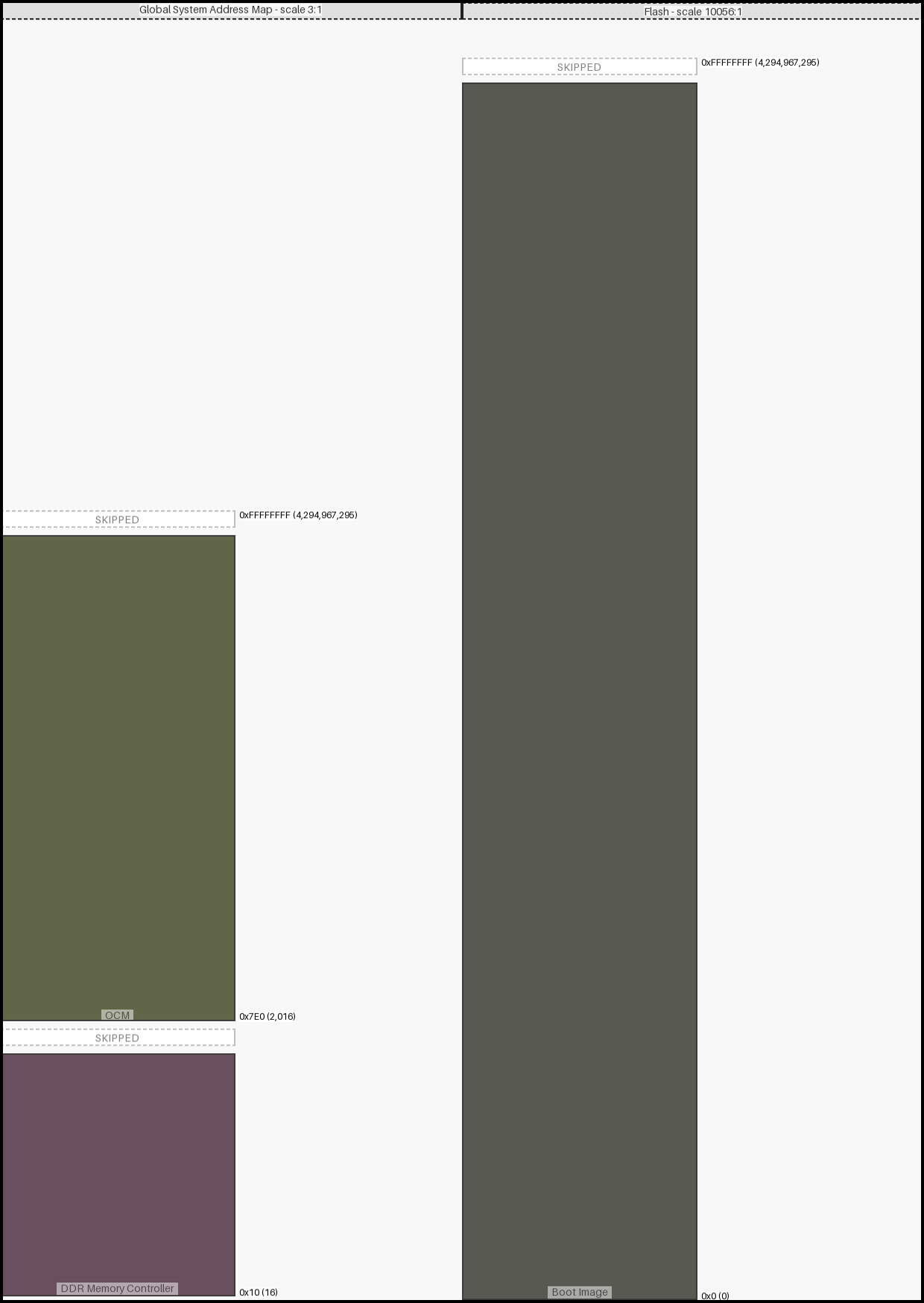

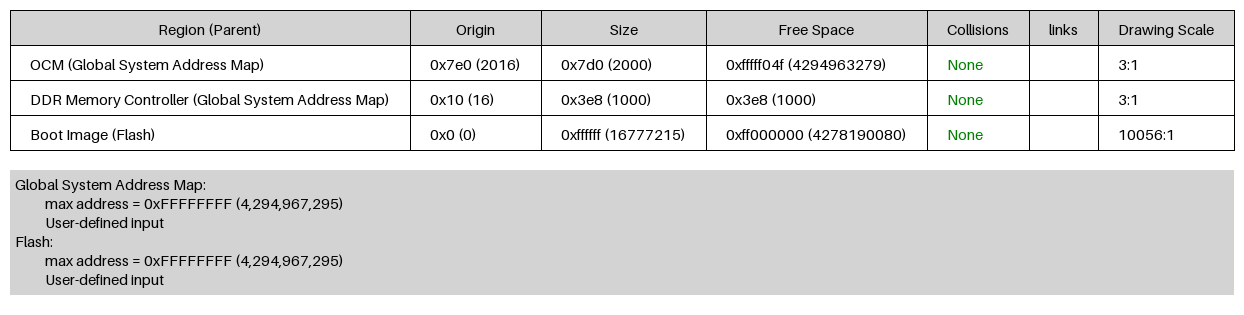

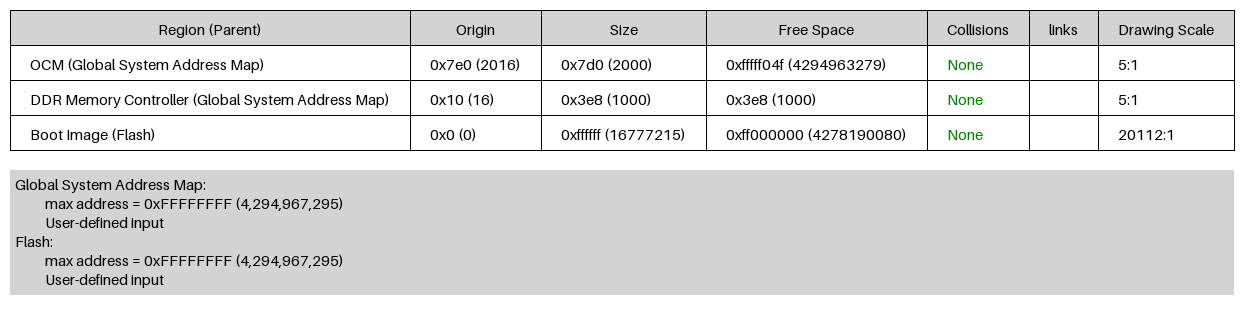

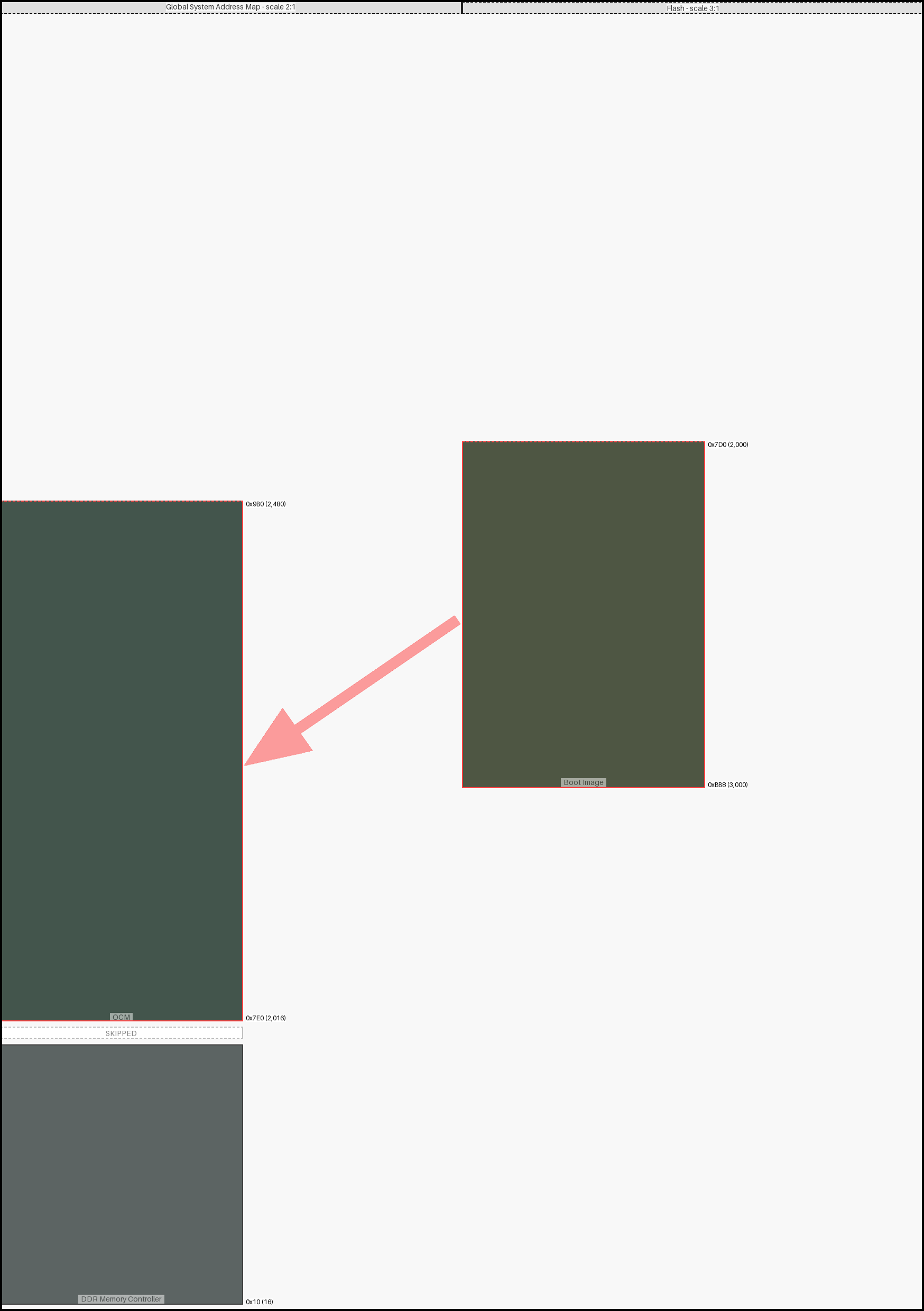

docs/example/example_three_maps |

| Diagram with three memory maps |

|

|

docs/example/example_three_maps.json

{

|

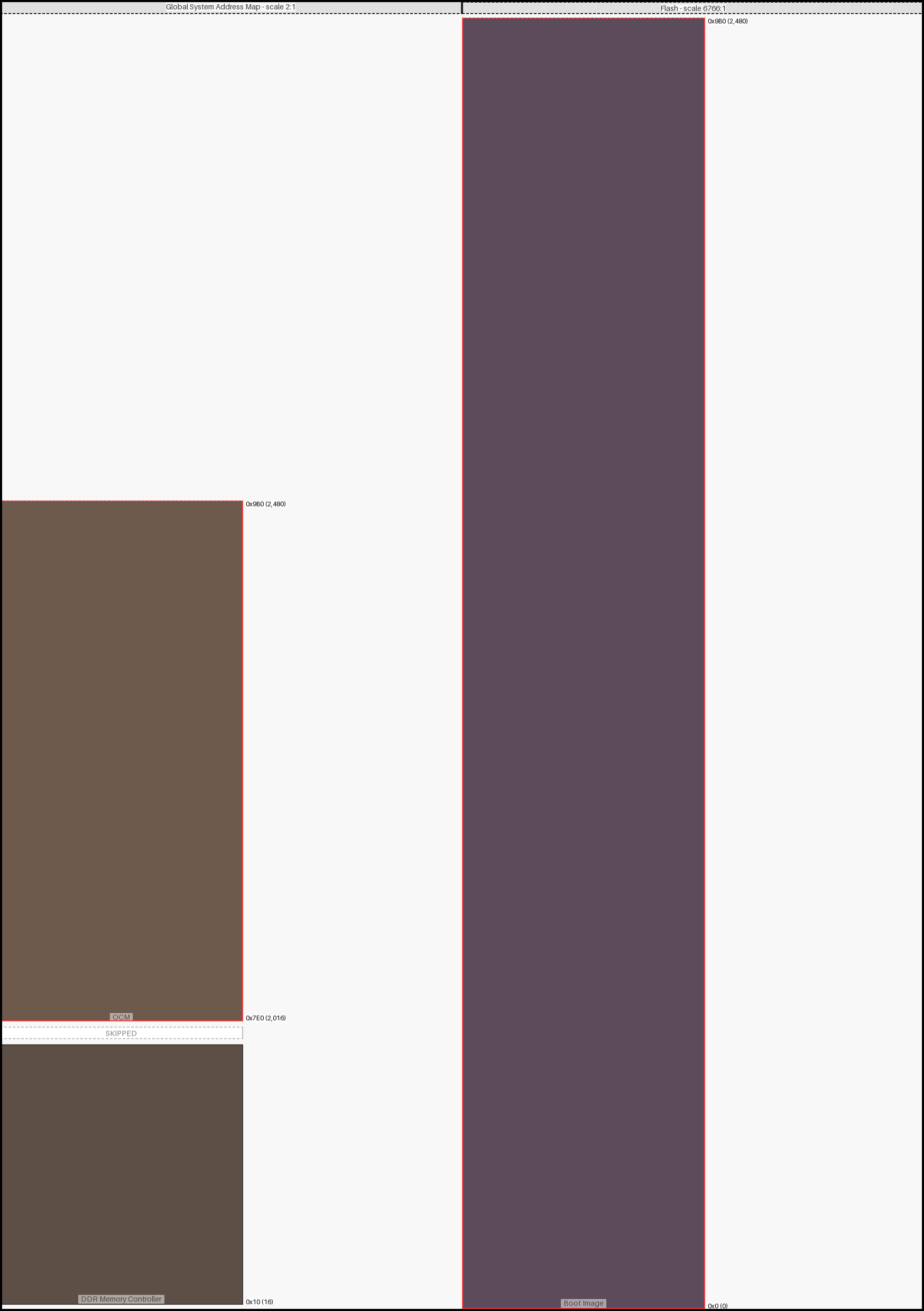

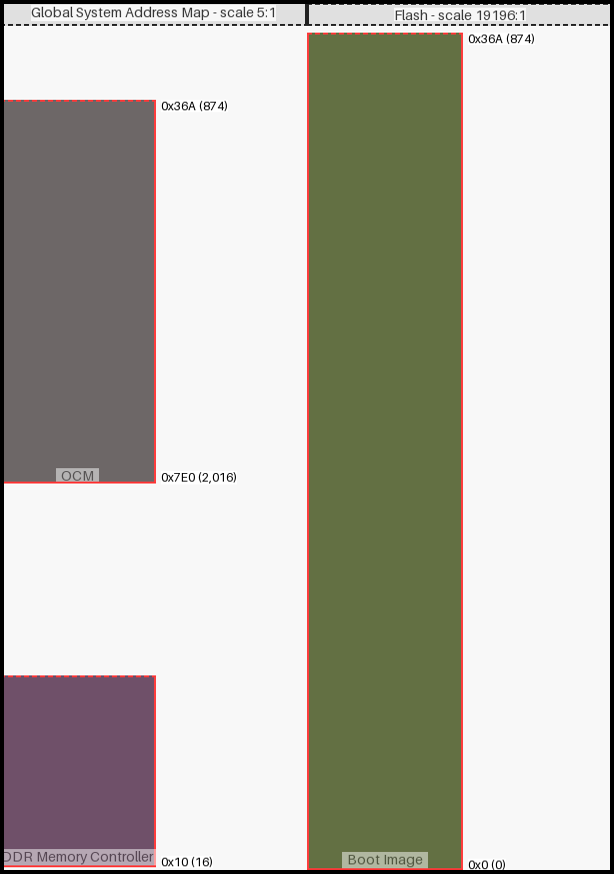

docs/example/A3_region_exceeds_height_no_maxaddress_set |

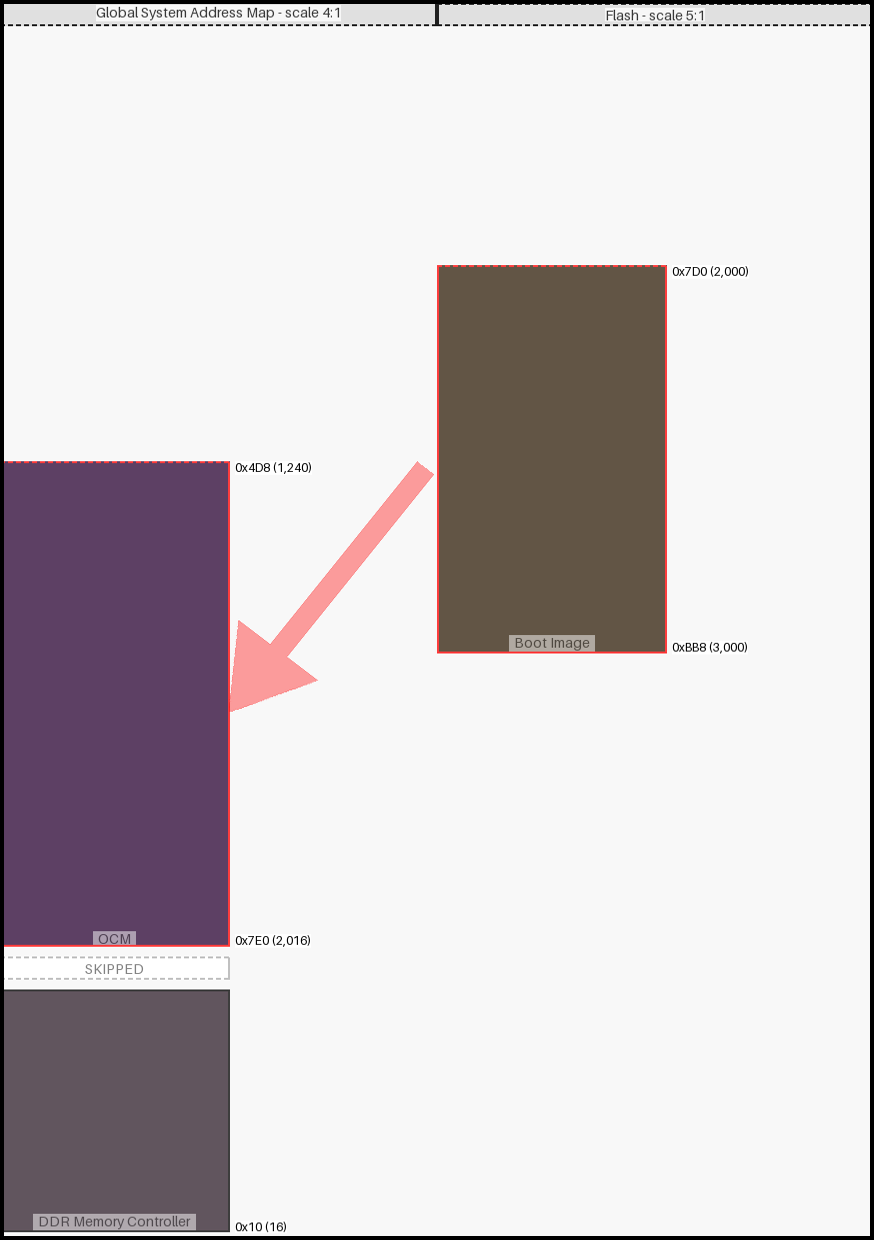

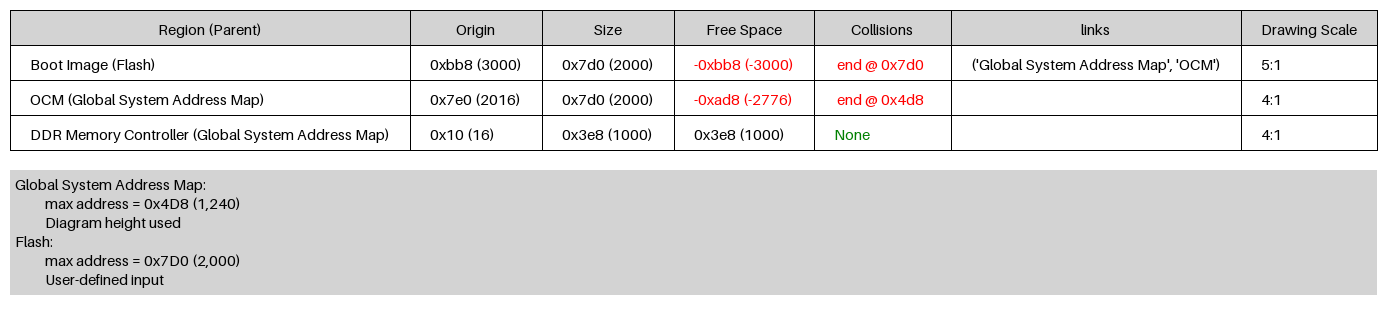

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A3_region_exceeds_height_no_maxaddress_set.json

{

|

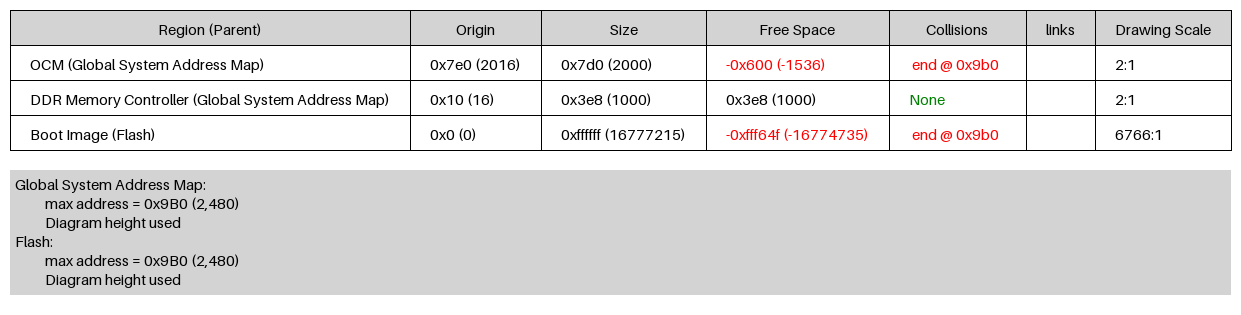

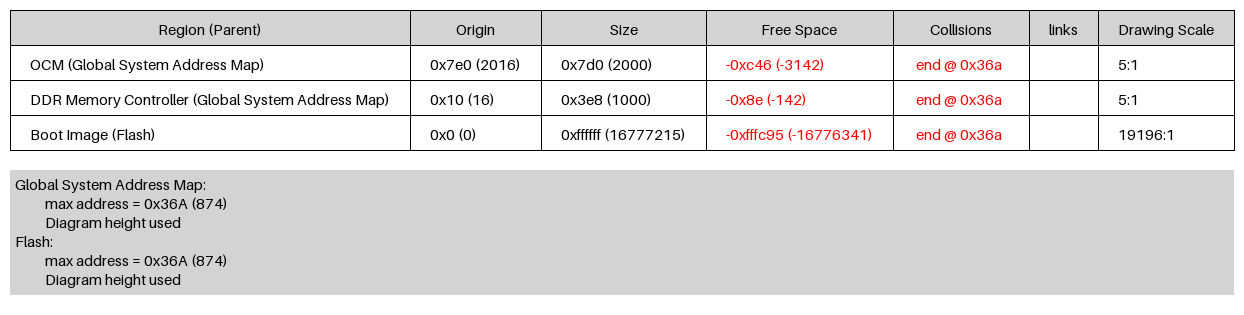

docs/example/A4_region_exceeds_height_no_maxaddress_set |

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A4_region_exceeds_height_no_maxaddress_set.json

{

|

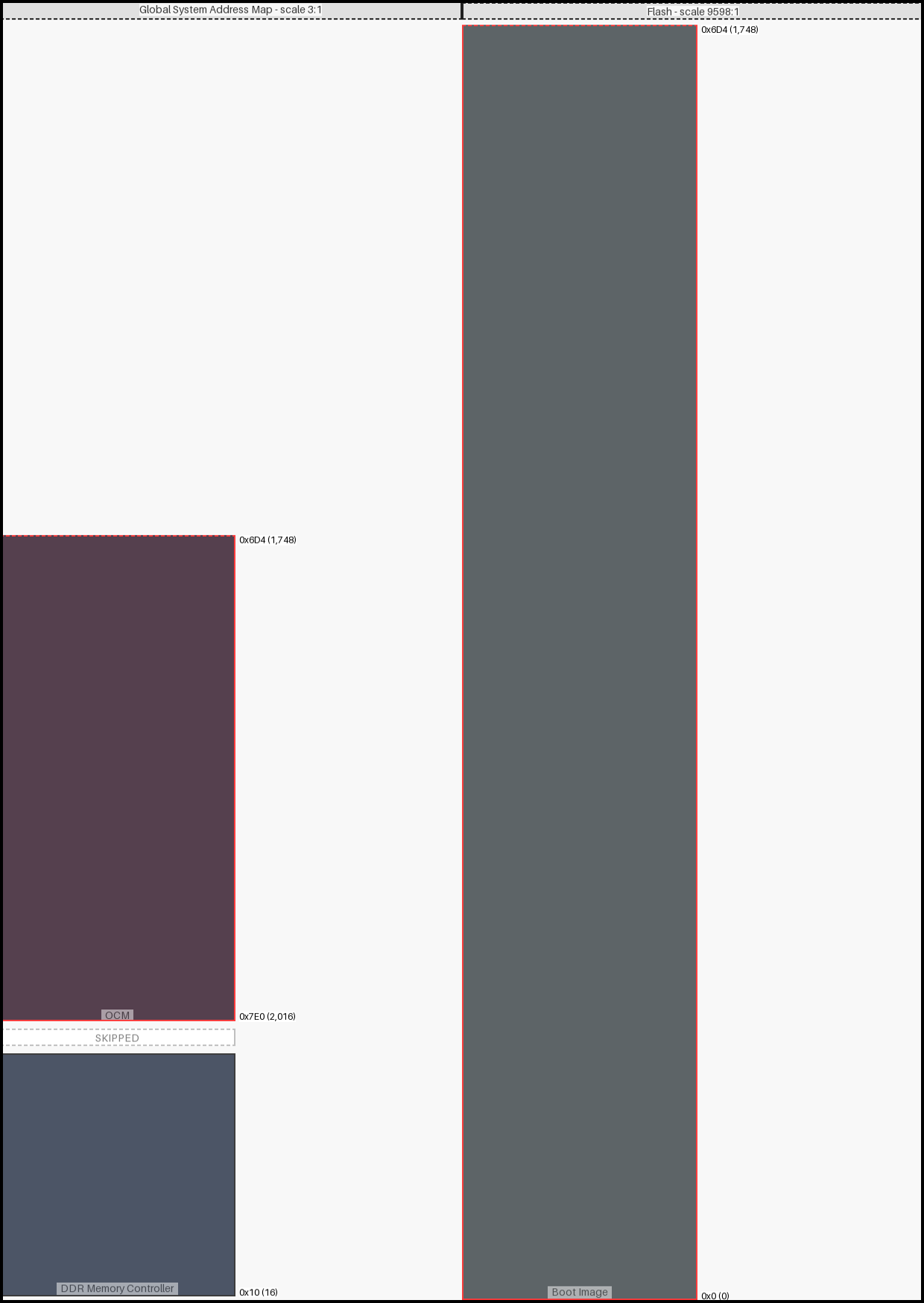

docs/example/A5_region_exceeds_height_no_maxaddress_set |

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A5_region_exceeds_height_no_maxaddress_set.json

{

|

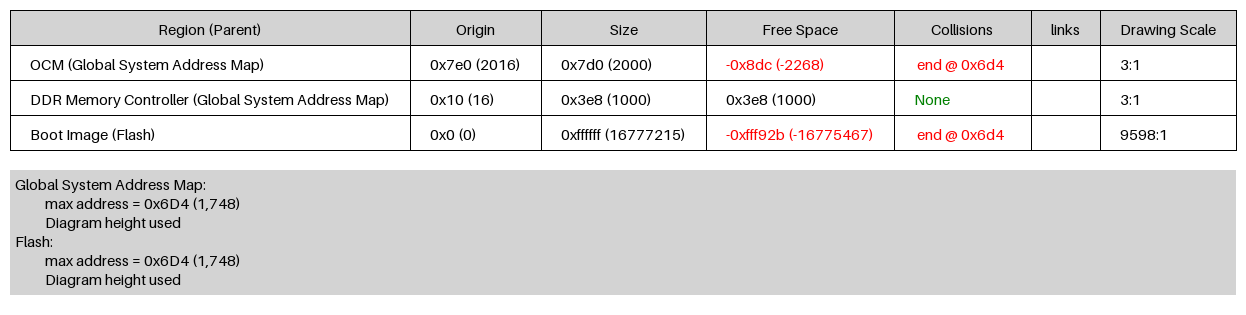

docs/example/A6_region_exceeds_height_no_maxaddress_set |

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A6_region_exceeds_height_no_maxaddress_set.json

{

|

docs/example/A7_region_exceeds_height_no_maxaddress_set |

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A7_region_exceeds_height_no_maxaddress_set.json

{

|

docs/example/A8_region_exceeds_height_no_maxaddress_set |

- region exceeds diagram height. Output should remain at page size but the drawing ratio will adjust to fit the larger contents Note the ratio is rounded up to nearest integer value. - Since the max_address was not set it was taken from the diagram height, which means the region collided with the max_address |

|

|

docs/example/A8_region_exceeds_height_no_maxaddress_set.json

{

|

docs/example/A3_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A3_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A4_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A4_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A5_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A5_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A6_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A6_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A7_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A7_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A8_region_freespace_exceeds_height_higher_maxaddress_set |

- 'max_address' is now set at a higher value than the max region size. This will cause excessive freespace values to be created (larger than the diagram height). To prevent illegible diagrams, the pre -calculated value will be used instead. NOTE: draw_scale is adjusted to allow for potential voidregions |

|

|

docs/example/A8_region_freespace_exceeds_height_higher_maxaddress_set.json

{

|

docs/example/A3_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A3_maxaddress_lower_than_memregions.json

{

|

docs/example/A4_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A4_maxaddress_lower_than_memregions.json

{

|

docs/example/A5_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A5_maxaddress_lower_than_memregions.json

{

|

docs/example/A6_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A6_maxaddress_lower_than_memregions.json

{

|

docs/example/A7_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A7_maxaddress_lower_than_memregions.json

{

|

docs/example/A8_maxaddress_lower_than_memregions |

- 'max_address is now set below the memregions but this will be overridden with the calculated largest value from the region data. |

|

|

docs/example/A8_maxaddress_lower_than_memregions.json

{

|